文化賦能品牌 廣州專業(yè)設(shè)計公司如何引領(lǐng)文旅與茶業(yè)新潮流

在文化創(chuàng)意產(chǎn)業(yè)蓬勃發(fā)展的今天,專業(yè)的設(shè)計公司已成為品牌塑造與市場拓展的核心驅(qū)動力。廣州,作為中國設(shè)計的前沿陣地,匯聚了一批專注于文化品牌打造的設(shè)計力量,尤其在文旅品牌策劃、茶葉品牌設(shè)計與文化產(chǎn)品營銷領(lǐng)域展現(xiàn)出卓越的創(chuàng)新能力。

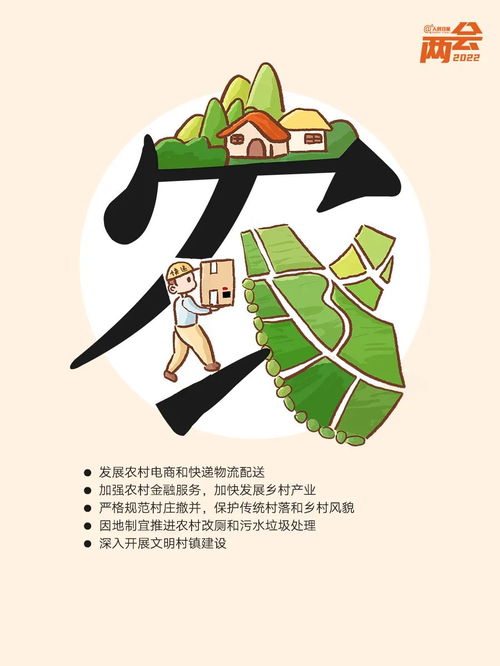

一、文旅品牌策劃與特色小鎮(zhèn)VI設(shè)計:講述在地故事

優(yōu)秀的文旅品牌策劃遠(yuǎn)不止于視覺美化,它是對一個地區(qū)歷史、人文與自然資源的深度挖掘與創(chuàng)造性轉(zhuǎn)化。廣州的設(shè)計公司擅長通過系統(tǒng)的VI(視覺識別)設(shè)計,為特色小鎮(zhèn)、旅游景區(qū)注入獨(dú)特的靈魂。從標(biāo)志、色彩到應(yīng)用物料,設(shè)計構(gòu)建一套連貫的視覺敘事體系,將抽象的文化內(nèi)涵轉(zhuǎn)化為可感知、可記憶的品牌形象,從而提升旅游目的地的辨識度與吸引力,推動地方文化的傳承與商業(yè)價值的共贏。

二、茶葉VI設(shè)計與茶包裝創(chuàng)新:連接傳統(tǒng)與現(xiàn)代

中國茶文化底蘊(yùn)深厚,但要在當(dāng)代市場脫穎而出,離不開專業(yè)的品牌設(shè)計與營銷策劃。廣州的茶葉VI設(shè)計公司深諳此道,它們不僅為茶企打造高雅、富有文化質(zhì)感的視覺形象,更在茶包裝設(shè)計上大膽創(chuàng)新。通過融合傳統(tǒng)美學(xué)元素與現(xiàn)代設(shè)計語言,創(chuàng)造出既體現(xiàn)茶道精神又符合當(dāng)下審美與實(shí)用需求的包裝,成為產(chǎn)品在貨架上無聲的推銷員。結(jié)合線上線下整合營銷策略,幫助茶葉品牌講好品牌故事,拓寬銷售渠道,實(shí)現(xiàn)從“產(chǎn)品”到“品牌”的跨越。

三、家族傳承設(shè)計與文化深度挖掘

對于擁有悠久歷史的家族企業(yè)或老字號品牌而言,傳承與創(chuàng)新同樣重要。專業(yè)的設(shè)計公司能夠介入“家族傳承設(shè)計”領(lǐng)域,通過梳理家族歷史、提煉核心精神,將其轉(zhuǎn)化為一套可持續(xù)的品牌資產(chǎn)與視覺體系。這不僅是對過去的致敬,更是面向未來的品牌煥新,確保文化遺產(chǎn)在商業(yè)演進(jìn)中保持活力與相關(guān)性。

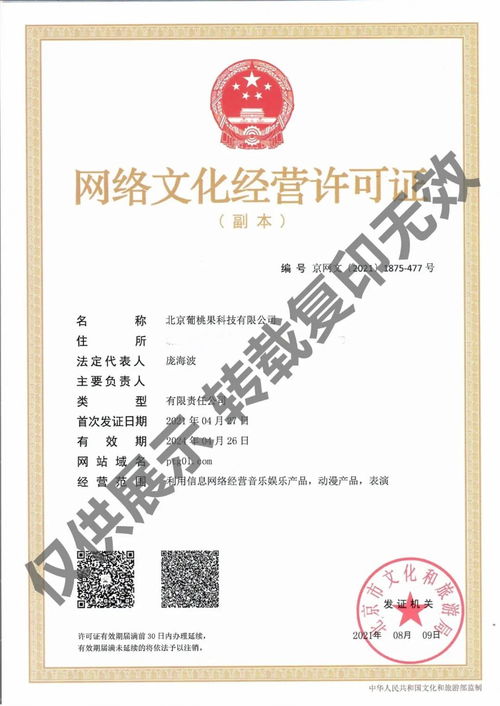

四、整合網(wǎng)絡(luò)文化經(jīng)營與營銷新陣地

在數(shù)字化時代,“網(wǎng)絡(luò)文化經(jīng)營”已成為品牌與消費(fèi)者溝通的重要橋梁。廣州的設(shè)計與策劃公司通常具備整合能力,將線下扎實(shí)的品牌基礎(chǔ)與線上活躍的社交媒體營銷、內(nèi)容創(chuàng)作相結(jié)合。通過策劃線上文化事件、打造網(wǎng)紅IP、運(yùn)營社群等方式,在數(shù)字空間構(gòu)建品牌的文化影響力,實(shí)現(xiàn)精準(zhǔn)營銷與粉絲沉淀,為文旅項(xiàng)目和茶品牌等帶來持續(xù)的關(guān)注與流量。

從文旅地標(biāo)的整體策劃,到一杯茶的包裝細(xì)節(jié),再到網(wǎng)絡(luò)空間的互動傳播,廣州的專業(yè)設(shè)計公司正以其深厚的文化理解力、前瞻的市場洞察力和精湛的設(shè)計執(zhí)行力,全方位賦能品牌。它們不僅是視覺的塑造者,更是文化價值的翻譯官與商業(yè)成功的戰(zhàn)略伙伴,共同推動著中國文化創(chuàng)意產(chǎn)業(yè)向更高品質(zhì)、更具影響力的方向邁進(jìn)。

如若轉(zhuǎn)載,請注明出處:http://www.txw7584.cn/product/60.html

更新時間:2026-04-14 13:39:43